RooKie_Z P7 基于Verilog CPU的MIPS微体系设计文档

写在前面

这是RooKie_Z的P7基于Verilog CPU的MIPS微体系设计文档,在课上测试中本CPU取得了 满分💯的成绩。

总体设计概述

本次要求实现的指令集为add, sub, and, or, slt, sltu, lui,addi, andi, ori,lb, lh, lw, sb, sh, sw,mult, multu, div, divu, mfhi, mflo, mthi, mtlo,beq, bne, jal, jr,mfc0, mtc0, eret, syscall ,在P6的基础上新增加了mfc0, mtc0, eret, syscall。

CPU部分与P6相比添加了重要模块CP0协处理器,其余的端口定义和转发、阻塞规则与P6相同,详见附带的P6设计文档,在此处不再赘述

考虑到宏观PC的处理,我把CP0协处理器放置在了M级

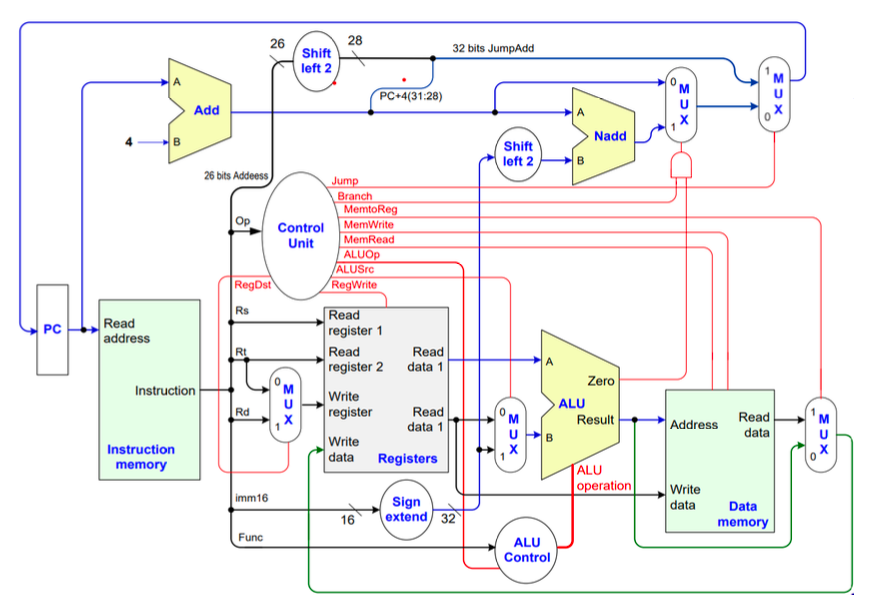

数据通路

添加转发后的数据通路

CP0插入流水线与异常码流水

做这样设计的原因如下:

我们称M级为宏观级. F, D, E级的指令”未曾执行”, M级指令“正在执行”, W级指令“执行完毕”. 相当于把流水线CPU封装为一个单周期 CPU.